关于时钟波形发生器的设计报告

话题:关于时钟波形发生器的设计报告

问题详情:求一篇关于时钟波形发生器的设计报告… 等…

回答:波形发生器设计报告一、 设计任务设计 一个波形发生器,该波形发生器能产生正弦波、方波、三角波和由 的特定形状波形。二、 设计要求1. 基本要求具有产生正弦波、方波、三角波三种 期性的波形。用键盘输入 生成上述三种波形(同 期)的线性组合波形,以及由基波及其谐波(5次以下)线性组合的波形。具有波形存储功能。输出波形的频率为100Hz~20KHz(非正弦波频率按10次谐波计算):重复频率可调,频率步进间隔≤100Hz。输出波形幅度范围0~5V(峰-峰值),可按步进0.1V(峰-峰值)调整。具有显示输出波形的类型、重复频率( 期)和幅度的功能。2.发挥部分输出波形频率范围扩展至100Hz~200KHz。

话题:求单片机时钟 设计

问题详情:请问有有单片机时钟的设计原理图和程序吗

回答:你要的是什么?是想要用单片机做一个电子表还是要单片机内部的定时器模块结构?

参考回答:LED电子钟( ATC2051) 时间:200-- 浏览:24 作者:佚名 LED电子钟在很多电子报刊杂志上都可以见到,但大多数在

话题:求专家发给我一 数字时钟电路的设计图,就是具体的电路

回答:好的,有了发给你

参考回答:只能给你一个设计的参考 。 数字电子钟的设计(由数字IC构成) 一、设计目的 1. 熟悉集成电路的引脚安排。 2. 掌握各芯片的逻辑

话题:求单片机时钟 设计

问题详情:请问有有单片机时钟的设计原理图和程序吗

回答:你要的是什么?是想要用单片机做一个电子表还是要单片机内部的定时器模块结构?

参考回答:LED电子钟( ATC2051) 时间:200-- 浏览:24 作者:佚名 LED电子钟在很多电子报刊杂志上都可以见到,但大多数在

话题:单片机时钟电路怎么做

回答:PCB布线 在PCB设计中,布线是完成 设计的重要步骤,可以说前面的准备 都是为它而做的, 在整个PCB中,以布线的设计过程限定最高,技巧最细、 量最大。PCB布线有单面布线、 双面布线及多层布线。布线的方式也有两种:自动布线及交互式布线,在自动布线之前, 可以用交互式预先对要求比较严格的线进行布线,输入端与输出端的边线应避免相邻平行, 产生反 干扰。必要时应加地线隔离,两相邻层的布线要互相垂直,平行容易产生寄生耦合。 自动布线的布通率,依赖于良好的布 ,布线 则可以预先设定, 包括走线的弯曲次数、导通孔的数目、步进的数目等。一般先进行探索式布经线,快速地把短线连通,

参考回答:你是要程序还是电路或是思路?

话题:用单片机设计 一 个时钟电路

问题详情:第位显示秒,初始时间为10时00分00秒。实在是不怎么会编

回答:你好 是用 C 还是汇编,私信 你了

参考回答:你要是会的话,我的程序发你可以按你的要求改下

话题:奥数 时钟问题

回答:关于时钟问题的探讨 作者:未知 无沦是用离散逻辑、可编程逻辑,还是用全定制硅器件实现的任何数字设计,为了成功地 作, 的时钟是非常关键的。设计 的时钟在极限的 度、电压或制造工艺的偏差情况下将导致错误的行为,并且调试困难、花销很大。 在设计pld/fpga时通常采用几种时钟类型。时钟可分为如下四种类型:全 时钟、门控时钟、多级逻辑时钟和波动式时钟。多时钟系统能够包括上述四种时钟类型的任意组合。 1.全 时钟 对于一个设计项目来说,全 时钟(或同步时钟)是最简单和最可预测的时钟。在pld/fpga设计中最好的时钟方 是:由专用的全 时钟输入引脚驱动的单个主时钟去钟控设计项目中的每一个触发

话题:利用单片机ATC51与ADC00设计 一个数字电压表,能够

问题详情:谁有啊 急求

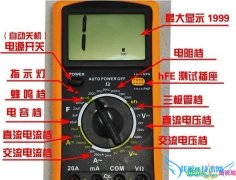

回答:本文介绍了用ADC00集 压转换芯片和ATC51单片机设计 的数字直流电压表。在测量仪器中,电压表是必须的,而且电压表的好坏直接影响到测量精度。具有一个精度高、转换速度快、性能稳定的电压表才能符合测量的要求。为此,我们设计了数字电压表,此作品主要由A/D00 和单片机ATC51构成,A/D 在单片机的控制下完成对模拟信号的采集和转换功能,最后由数码管显示采集的电压值。此设计通过调试完全满足设计的指标要求。电路 设计简单,设计 方便有较强的实用性。关键词:ADC00;单片机ATC51;数字电压表Abstract: In this paper, with ADC00 voltage converter integrated chips and

参考回答:发个程序大家看看:#include reg52.h#include absacc.h#include intrins.h#include string.h#include math.hbit flag;unsigned

话题:"如何使用50MHZ

问题详情:1、首先 有一个CPLD―50 不然就会和其他时钟产生偏移,

回答:"PLL当然是最准确 的办法,但是要外接压控振荡源,那玩意不太好做的。有一个思路:采用计数器进行乘除运算。大致的作法是:1、先用一个10进制的计数器,逢10进1,就相当于除以10,可以得到5MHz的脉冲;举例来说,你可以在CPLD里面直接调用一个4LS145就成了。2、再用一个5进制计数器,就相当于除以5,得到1MHz。或者直接就设计 一个1/50的计数器,更简单一点。3、然后反向 作,乘上3。具体要用哪种计数器或者触发器,我一下子也想不起来了,太久没玩数字电路了,呵呵。"

参考回答:"没有PLL或者是外置电路是做不到的。可以输出1MHz方波,然后用RC滤波器把3MHz的成分滤出来再放大。如果是用FPGA,直接用

话题:利用51单片机扩展相关的 电路,设计 一个倒计时时钟

问题详情:利用51单片机扩展相关的 电路,设计 一个倒计时时钟,该时钟

回答:#includereg52.h#define uchar unsigned char#define uint unsigned intunsigned char code duma[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0xd,0x0,0xf,0x6f}; 0-数码管,共阴unsigned char code wema[]={0xf0,0xf1,0xf2,0xf3,0xf4,0xf5,0xf6,0xf}; 片选,1-个数码管uchar i;uint number;uchar qian,bai,shi,ge;void delay(uchar x){ uchar a,b; for(a=x;a0;a--) for(b=100;b0;b--);}void inter_init(){ EA=1; 开总中断 ET0=1; 本例中使用的是定时器T0,如果用T1。则为ET1=0,TMOD=0x10。 TMOD=0x01; 定时器 方式1 TH0=(65535-50000)/256; 因为晶振用的是11.052MHZ。在取初值时,大概定义为一个中断为50MS TL0=(65535-50000)%256; TR

参考回答:这种设计估计没人帮得了你。像前面这位 ,连人家电路怎么接的都不知道程序就出来了。我估计你看不懂程序的话,他的程序你也

- 评论列表(网友评论仅供网友表达个人看法,并不表明本站同意其观点或证实其描述)

-