单片机晶振电路中-小知识

话题:单片机晶振电路中,无源晶振的外壳有必要接地吗?

问题详情:各位高人,请问无源晶振的外壳究竟有没有必要接地?我最近弄了

回答:晶振让你那么长时间的拿烙铁烙都给烧坏了!!!!其实晶振这个东西本来就有误差的!所以没有必须壳接地!!!

话题:晶振外壳如何接地?

问题详情:晶振 接地的目的是抗干扰,我们目前用的是园柱型直 封装,如果

回答:可以采用捆绑接地,用元器件引脚将晶振捆绑,然后把元器件引脚接地

话题:请问金属外壳的晶振做单片机时钟时,晶振的外壳是否要接

回答:可以不接地。但有的设计考虑到对晶振外的高频干扰的屏蔽。一般都让外壳接GND。 一般是画PCB板的时候,在晶振外壳附近大面积覆铜,覆铜就接GND。覆铜靠近晶振两引脚中间偏外的地方放置一个不通孔的TOPLAYER的焊盘接覆铜上即可。焊接的时候,在晶振靠近这个焊盘的外壳打磨一下(以便下焊锡),点焊锡焊上即可。

话题:音叉晶振,除了两个焊脚外,外壳接地会影响性能么?或者说

回答:最好做外壳接地。机箱对地有110伏,接了地线就没有了,这样就不会有触电的感觉,但是如果要是打雷的时候,有了接地电脑就会坏的更厉害的。 这种现象绝对不可能出现,有了接地线打雷会坏的更厉害,那什么电器都不敢接地了,那么避雷线,避雷带都不能用了.应该说如果接地电阻不和要求,会影响接地的效果

参考回答:建议外壳接地

话题:Launchpad G2553 外部晶振很奇怪的一个现象!!求助 狗

问题详情:注意图中外部晶振的头和方形焊盘焊接固定起来了,测试外部

回答:方形焊盘 一般作用是接电屏蔽晶体干扰和固定作用!以前遇到过烙铁 度过高的时候固定晶体时 容易损坏晶体,楼主看下是不是这个问题~~呵呵

参考回答:晶振外壳接地,是为了抗干扰。有时不接地也没问题。你的晶振是不是被你用烙铁烫坏了~~

话题:创新A5的SB0声卡,右侧晶振上有手工状态的焊锡和锡

问题详情:新买的SB0声卡,在右边晶振的位置上有明显的一块手工焊锡

回答:对于要求较高的设计,在设计时就考虑晶振的外壳接地,一般采用晶振三引线(中间一条引线是接地的),或外壳上加个金属外套接地,但这样会增加晶振的采购成本,因此在没有预留设计位置时,有的就直接把晶振外壳采用你图中所示方法接地。只要不与晶振任一引线造成短接,使用没什么影响,甚至有利于对晶振的 。

话题:单片机晶振偶尔停振是怎么回事?

问题详情:单片机晶振偶尔停振,然后又重新起振,这是什么原因造成的?

回答:芯片或外接电容的问题,还有晶振要尽量靠近单片机!

参考回答:芯片或外接电容的问题,还有晶振要尽量靠近单片机!

话题:两层PCB晶振在顶层,且有数字地覆铜,底层能走高频信号线

问题详情:16M表贴晶振

回答:16m的表贴外壳接地 会好点 但是这个东西真不好说 我们这边做法一般是 做跳线 然后将那根线用跳线贴板子走 如何不会有影响 然后定板子 然后量产

话题:为什么会引起AM2主板上晶振坏?

问题详情:以为BIOS坏了就 了一下,后来还是这样,检测最终发现晶振坏

回答:如果第三次发现是因为晶振“坏”而引起故障的话,才能确认是晶振的附设电路的问题;现在的可能性是,新换的晶振可能原来就特性 ,或者是在使用一段时间之后变值;也可能是在焊接晶振时没有将手先放电,或者电烙铁外壳没有接地,导致新换的晶振带有某些“疾?钡囊?迹?ぷ饕欢ǖ氖奔浜蠹词?Щ虮渲怠

参考回答:晶振损坏查供电,你的电源是什么?

话题:为尽量减少电磁干扰,在设计PCB过程中应注意什么问题?

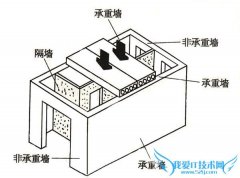

回答:数字电路抗干扰设计 在电子系统设计中,为了少走弯路和节省时间,应充分考虑并满足抗干扰性的要求,避免在设计完成后再去进行抗干扰的补救措施。形成干扰的基本要素有三个: (1)干扰源,指产生干扰的元件、设备或信号,用数学语言描述如下:du/dt,di/dt大的地方就是干扰源。如:雷电、继电器、可控硅、电机、高频时钟等都可能成为干扰源。 (2)传播路径,指干扰从干扰源传播到敏感器件的通路或媒介。典型的干扰传播路径是通过导线的传导和空间的辐 。 (3)敏感器件,指容易 扰的对象。如:A/D、D/A变换器,单片机,数字IC,弱信号放大器等。 抗干扰设计的基本原则是:抑制干扰源,切断干扰传播路径,提高敏感器件

- 评论列表(网友评论仅供网友表达个人看法,并不表明本站同意其观点或证实其描述)

-