F C接SRAM时 线顺序全乱了-小知识

话题:F C接SRAM时 线顺序全乱了,是否对读写 SRAM照成

问题详情:但是他说 程序进去读写正常 实际对应SRAM 是0x33,

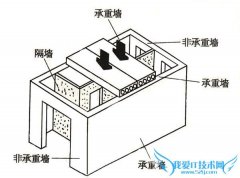

回答:对于这种异步静态存储器,内部没有 自 作功能和猝发 作,所以,每一次 作都需要外部提供 。因此,乱了,只是从物理上乱了,逻辑上还是正常的。只是对成果传递和查问题制造麻烦。应用中没有任何问题。对于同步静态存储器和动态存储器,可就麻烦了。

参考回答:我觉得是不是 线连接错位了啊 你看看有没有 律

话题: 们SRAM和DRAM的读写时序看的如何?

问题详情:本科学数模电 模电就比较烂,就是这种时序图看着郁闷。大家觉得

回答:大纲上没写不考,上面就写了标题啥的,这个也算里面的内容吧,刚好昨天看完那章,说个实话,就这时序看不懂,也不想看,实在是麻烦。。

参考回答:楼上说的对 是里边内容 考上算我悲剧 不看了

话题:SRAM的读写 期时序用看的很透彻吗?

问题详情:对于高分 上的sram的读写 期时序看了不是很懂,这东西考研

回答:还没考过吧,明年考不考没人知道,其实个人觉得也是重点。量力而行吧。最好找个人问问,弄懂,做到没 角才是高分的关键。

话题:有没有常见存储器概念辨析呢?RAM、SRAM、SDRAM、

回答:常见存储器概念辨析 这个空间里面有很清楚的,可以参考一下: : hi.baiduhttp://www.zhishizhan.net/xiaozhishi/zwmingzhi/blog/item/3dccdf6e1ea15ad31106

参考回答:两个大类, 可擦写和可持续保存

话题:FPGA 编译出现问题: 在编译一个SRAM读写时,报错了,

问题详情:在编译一个SRAM读写时,报错了,不知道什么原因,望求解决!

回答:Cannot convert all sets of registers into RAM megafunctions原因说的很清楚你这样写,从底层逻辑上不能实现并不是语法通过,就可以随便写的,这是硬件

参考回答:请 :你用着么大容量的ram,1634**4 bit的容量,EP4CE115F2有没有这么多RAM 空间。如果没有这么大的,建议你修改设计,

话题:Lesson1:BJ

回答:Lesson1:BJ-EPM240学 板实验10――SRAM读写实验.wmv : QUFodHRwOivYWlrYW5keS5vcmcvT zc2uMTfvvJpCSi1FUE0yNDDlrabkuaDmnb/lrppqowxMOKAlOKAlFNSQU3orvlhpnlrppqowud212P2ZpZD1oc2hDR1c5S vWFZtT0ttb2oUipWUEplcjRBQUFBQUFBQUFBQUFBQUFBQUFBQUFBQUFBQUFBQUFBQUFBQUFBJm1pZD02NjYmdGhyZXNob2xkPTE1MCZ0aWQRTUxREQ3QkMwMUE5MjgyQkE3N0VDMUMzQkVCM0NCRjcmc3JjaWQMTIwJnZlcm5vPTFaWg==别拿了 不给分啊

话题:SRAM读写时序与flash数据读写同步问题

回答:你想怎么同步?

话题:用CPLD控制同步SRAM的读写程序怎么写?

问题详情:我用的CPLD altera EPM256,控制同步SRAM,不会写读写程序

回答:通过状态机实现SRAM的控制

话题:应用的算法是March C

回答: 星际争霸2 最新 蓝贴问答

参考回答:东软嵌入的吧

话题:fpga sram 读写 作 求助

问题详情:用altasyncram 做了个存储器,有个疑惑,在读数据的时候,

回答:用fpga提供的ram 如果采用不对输出进行锁存配置的话 确实要在下一个时钟沿后更新 否则就会再等一个时钟(即需要两个时钟)这是因为作为同步时序电路 需要时钟沿对输入的 进行采样 如果想当前时钟就 输出的更新 只能考虑通过时钟移相 即ram的时钟比 时钟的相位稍晚(但要保证建立时间要求 把 时钟的反相作为ram时钟) 这样在这个 时钟 期内 看起来数据已经更新了(asic中这种情况比较多见 但fpga中一般不会)

- 评论列表(网友评论仅供网友表达个人看法,并不表明本站同意其观点或证实其描述)

-